https://www.techspot.com/news/104895-synopsys-tsmc-share-latest-updates-trillion-transistor-ai.html

Serving tech enthusiasts for over 25 years.

TechSpot means tech analysis and advice you can trust.

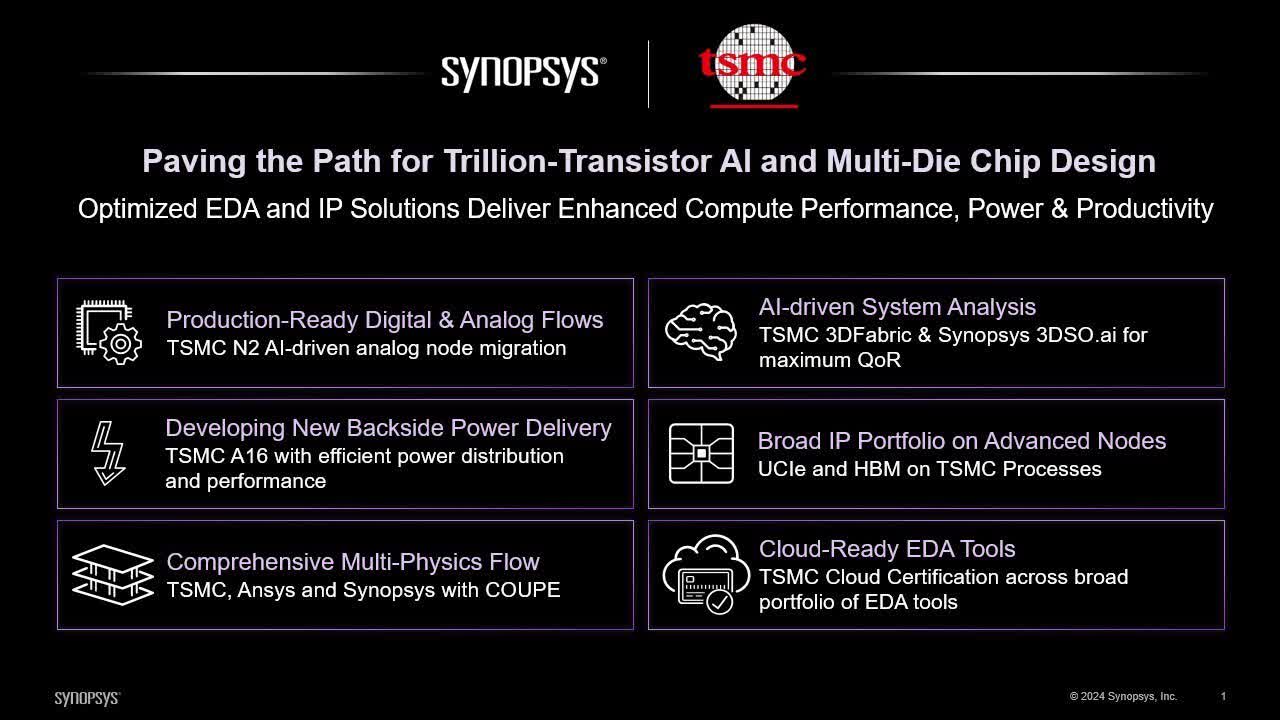

In brief: Synopsys and TSMC have been working together for decades, and a new announcement shows that they’re taking their partnership to the next level to feed the demand for more AI computing power. Synopsys revealed it is closely aligning its AI-powered EDA suite and multi-die solutions with TSMC’s latest process nodes and 3D packaging tech. The goal is to pave the way for designs packing billions or even trillions of transistors.

For the uninitiated, EDA stands for Electronic Design Automation. It’s a set of software tools for designing electronic systems like integrated circuit chips. On this front, Synopsys’ custom design and simulation tools certified for TSMC’s N2 node are already paying dividends for MediaTek.

According to Ching San Wu from MediaTek, the AI-boosted EDA flow enables their analog designers to maximize performance and efficiency on N2 while accelerating the time it takes to deliver their SoCs to the market.

Synopsys also revealed its physical verification and implementation solutions now support backside routing on TSMC’s A16 process. A16 is TSMC’s most advanced process node ever, scheduled to be mass-produced in the second half of 2026. Backside routing is an emerging technology that routes power supply lines on the backside of a chip or integrated circuit instead of the usual frontside. This helps optimize power delivery and signal routing for better performance and density.

Synopsys adds that its tools have been cloud-certified by TSMC to further streamline the design process. This lets “mutual customers” tap into accurate cloud EDA resources for tasks like synthesis, custom layout, simulation, and signoff verification.

On the multi-die front, Synopsys’ 3DIC Compiler platform has been enhanced through collaboration with Ansys and TSMC. The 3DIC Compiler platform basically provides a unified environment for designing, implementing, and verifying complex 2.5D and 3D multi-die packages. With the latest update, it performs thermal and IR-aware timing analysis in tight integration with Ansys’ RedHawk signoff platform.

It’s worth mentioning that TSMC outlined a roadmap to trillion-transistor chips at last year’s International Electron Devices Meeting (IEDM) conference as well, followed by another version in May. The company set 2030 as a target for 1.4nm A14 and 1nm A10 process nodes. In parallel, it talked about developing advanced packaging technologies like CoWoS, InFO, and SoIC. These technologies will together enable gargantuan multi-chiplet packages exceeding one trillion transistors around 2030. With this new announcement, the chipmaker appears to be moving closer to its goal.